مجلة جامعة طرطوس للبحوث والدراسات العلمية \_ سلسلة العلوم الهندسية المجلد (5) العدد(4) 2021

Tartous University Journal for Research and Scientific Studies - engineering Sciences Series Vol. (5) No. (4) 2021

## تصميم دارة جامع/طارح لاربع بت بالاعتماد على تقنية GDI باستخدام تقنيات تصنيع مختلفة

د.م. سوزي صالح\*

(تاريخ الإيداع 4/ 14 /2021 . قُبل للنشر في 9 /6 /2021 )

🗖 ملخّص 🗖

يتناول هذا البحث تصميصم وتحليل أداء دارة جامع/طارح لأربع بت Gate Diffusion Input (GDI). عملية التصميم تمت بعد رسم الخريطة الفيزيائية Layout للدارة بالاعتماد على عدة نقنيات لتكنولوجيا تصنيع الدرارات الالكترونية وهي: 65nm الفيزيائية Layout التقنيات التي اعتمدت عليها معظم الدراسات السابقة) بالإضافة التقنيتين الجديدتين وهما 32nm و 32nm و MICROWIND من أجل مقارنة مساحة الرقاقة والطاقة المستهلكة لكل تقنية باستخدام برنامج

كلمات مفتاحية: دارة جامع/طارح لاربعة بت، تقنية GDI، برنامج DSCH3.5، برنامج 3.5 MICROWIND.

<sup>\*</sup>أستاذ مساعد في كلية هندسة تكنولوجيا المعلومات و الاتصالات- قسم النظم الحاسوبية- جامعة طرطوس -

مجلة جامعة طرطوس للبحوث والدراسات العلمية \_ سلسلة العلوم الهندسية المجلد (5) العدد(4) 2021

Tartous University Journal for Research and Scientific Studies - engineering Sciences Series Vol. (5) No. (4) 2021

# Designe of 4 bit adder/ Subtractor Circuit using GDI technique using different fabrication techniques

Dr. ENG.Susi SALEH\*

(Received 14/4/2021. Accepted 9/6/2021)

#### $\square$ ABSTRACT $\square$

This paper focuses on designing and analyzing the performance of 4 bit adder/ Subtractor Circuit using based on Gate Diffusion Input (GDI) technology. The design process was done after drawing the the layout of the tow different topologies using several technology models as 65nm and 45nm (the techniques that used on most of the previous studies) as well as the new technologies 32nm and 22nm. The circuit was designed and simulated using DSCH3.5 software. Layout physical map drawing and simulation was done in order to compare chip area and energy consumed per technology using MICROWIND 3.5 software.

**Key words**: 4 bit adder/Subtractor Circuit, GDI Technology, DSCH 3.5, MICROWIND 3.5.

#### 1- مقدمـة

بسبب التطور الكبير في التكنولوجيا وظهور الأنظمة الرقمية ذات درجة عالية من التكامل (Very للبير في التكاولوجيا وظهور الأنظمة الرقمية ذات درجة عالية من الترانزستورات لحمن رقاقة صغيرة)، فقد توجب على المصممين مراعاة الامور التالية عند تصميم أي دارة: عدد الترانزستورات التي تدخل في تصميم الدارة، ومساحة الرقاقة المتاحة، واستهلاك الطاقة والتأخير الزمني، ومن هنا ظهرت الحاجة إلى تصميم دارات بطاقة منخفضة وسرعة عالية وأداء عال ومساحة رقاقة صغيرة[2][1].

تعد دارات الجامع الكامل FA (Fall Adder) و الطارح الكامل (Full Subtractor) من أهم المكونات في معظم الدارات الرقمية و دارات الحساب المعقدة مثل المعالجات الدقيقة أو معالجات الإشارات الرقمية أو معالجات الصور الرقمية، ووحدة الفاصلة العائمة وذاكرة التخزين المؤقت ووحدة الوصول إلى الذاكرة. كما أنها تعد الدارة الأكثر أهمية عند تصميم وحدة المعالجة المركزية فهي تعتبر بمثابة حجر الأساس في وحدة الحساب والمنطق ALU .

بناءً على ذلك، تم اقتراح العديد من دارات الجامع الكامل, و دارات الطارح الكامل (Full Subtractor) التي تراعي شروط التصميم VLSI مثل استهلاك الطاقة والتأخيرالممكن حدوثه في الدارة بكافة انواعه والمساحة المستخدمة لتصميم الدارة، ولكن تركزت معظم الدراسات على دراسة وتصميم دارة الجامع الكامل فقط أو الطارح فقط.

فقد قام الباحثون في [5-3] بتصميم دارات جامع FA تحتوي على عدد قليل من الترانزستور باستخدام تقنية ترانزستورات المرور (PTL) Pass Transistor Logic التي تسمح بتقليل استهلاك الطاقة، ولكن وعلى الرغم من بساطة هذه الدارات المقترحة، فإن التشوه الشديد في إشارة الخرج وعدم قدرتها على العمل بجهود منخفضة جعلها غير مجدية [6].

على الرغم من أن Static CMOS Logic كان منهج التصميم الأكثر انتشاراً على مدار العقود الثلاثة الماضية، فقد بُذلت العديد من المحاولات لاقتراح بديل أفضل لتحقيق استهلاك أقل للطاقة، ومساحة أصغر وأداء أفضل. من هذه الحلول تم تطبيق تقنية تصميم منخفضة الطاقة تدعى تقنية (GDI) -Gate Input من هذه التقنية بتقليل استهلاك الطاقة وتأخير الانتشار ومساحة الرقاقة. اهتم الباحثون بتصميم دارات الجامع الكامل وفق تقنية الـ GDI معتمدين على استخدام بوابات XNOR و دارة ناخب-11] MUX [15]، وقد استطاعت هذه الدراسات الوصول الى الغاية المطلوبة من حيث العدد المنخفض من الترانزستورات والاستهلاك المنخفض للطاقة والمساحة الاصغرية وقيمة تأخير منخفضة.

قام الباحثون بتصميم دارة طارح كامل بالاعتماد على FinFET حيث استطاعت هذه الدراسة تخفيض استهلاك الطاقة ولكن لم تأخذ بعين الاعتبار مساحة الشريحة المستخدمة [16].

قدم الباحثون تصميم دارة طارح كامل بالاعتماد على تقنية الـ GDI معتمدين على تكنولوجيا تصنيع الدرارات 150nm المحثول استطاعت هذه التقنية تحقيق استهلاك أقل للطاقة، ومساحة أصغر وأداء أفضل ، ثم قدم الباحثون دراسة تسمح بتحسين المساحة و استهلاك الطاقة لدارة طارح كامل كذلك بالاعتماد على تقنية الـ GDI ولكن بالاعتماد على تكنولوجيا تصنيع الدرارات mm 130 و 45nm و 45nm.

تم اقتراح دارة جامع طارح بالاعتماد على التقنيتين 65nm و45nm، ولكن هذه الدارسة لم تراعي مساحة الشريحة وعدد الترانزستورات المستخدمة [20] .

#### 2- هدف البحث

يتطرق في هذا البحث لدراسة وتصميم دارة جامع /طارح لاربع بت Layout في هذا البحث لدراسة وتصميم دارة جامع /طارح لاربع بت Gate Diffusion Input (GDI). ثم لرسم الخريطة لفيزيائية adder/subtractor بالاعتماد على عدة تقنيات لتكنولوجيا تصنيع الدرارات الالكترونية وهي: 65nm و 45nm و هذا البحث سنقوم باستخدام تقنيتين جديدتين هما 32nm و كذلك التي اعتمدت عليها معظم الدراسات السابقة، وفي هذا البحث سنقوم باستخدام تقنيتين جديدتين هما 22nm و كذلك 22nm

تم الاعتماد على برنامج DSCH3.5 من اجل محاكاة الدارة على مستوى الترانزستور، وتم الاعتماد على برنامج MICROWIND 3.1 من اجل رسم ومحاكاة الخريطة الفيزيائية

#### 3- طرائق البحث ومواده

## STATIC CMOS دارة الجامع الكامل بتقنية 1-3

دارة الجامع الكامل عبارة عن دارة متجانسة تقوم بحساب المجموع الحسابي لثلاث اشارات: المدخل (A) والمدخل (B) والمدخل (C) وهو الحمل من المرحلة السابقة. خرج دارة الجامع الكامل هو المجموع (SUM)، و الحمل الى المرحلة اللاحقة (Cout).

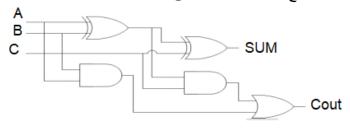

الشكل (1) يبين دارة جامع كامل لبت واحد على مستوى البوابات المنطقية

الشكل (1): دارة جامع كامل لبت واحد

والجدول (1) يبين جدول الحقيقة للدارة.

الجدول (1): جدول الحقيقة لدارة جامع كامل لبت واحد

| A | В | Cin | SUM | Cout |

|---|---|-----|-----|------|

| 0 | 0 | 0   | 0   | 0    |

| 0 | 0 | 1   | 1   | 0    |

| 0 | 1 | 0   | 1   | 0    |

| 0 | 1 | 1   | 0   | 1    |

| 1 | 0 | 0   | 1   | 0    |

| 1 | 0 | 1   | 0   | 1    |

| 1 | 1 | 0   | 0   | 1    |

| 1 | 1 | 1   | 1   | 1    |

المعادلات البوليانية التي توضح العلاقة ما بين مداخل ومخارج دارة جامع كامل لبت واحد هي:

$$SUM = A \oplus B \oplus C \tag{1}$$

$$Cout = A \cdot B + B \cdot C + C \cdot A$$

$$Cout = A \cdot B + C(A \oplus B)$$

(2)

## STATIC CMOS دارة الطارح الكامل بتقنية 2-3

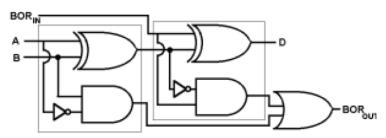

يبين الشكل (2) دارة طارح كامل لبت واحد على مستوى البوابات المنطقية

الشكل (2): دارة طارح كامل لبت واحد

والجدول (2) يبين جدول الحقيقة للدارة.

الجدول (2): جدول الحقيقة لدارة طارح كامل لبت واحد

| Input |   |       | Output |        |  |

|-------|---|-------|--------|--------|--|

| A     | В | BORin | D      | BORout |  |

| 0     | 0 | 0     | 0      | 0      |  |

| 0     | 0 | 1     | 1      | 1      |  |

| 0     | 1 | 0     | 1      | 1      |  |

| 0     | 1 | 1     | 0      | 1      |  |

| 1     | 0 | 0     | 1      | 0      |  |

| 1     | 0 | 1     | 0      | 0      |  |

| 1     | 1 | 0     | 0      | 0      |  |

| 1     | 1 | 1     | 1      | 1      |  |

المعادلات البوليانية التي توضح العلاقة ما بين مداخل ومخارج دارة طارح كامل لبت واحد هي:

$$BOROUT = BOR_{IN} (A'B' + AB) + A'B$$

(4)

Difference =

$$A \oplus B \oplus BOR_{IN}$$

(5)

#### 3-3 تقتية GDI:

انتشرت في الآونة الأخيرة نقنية (GDI) -Gat Diffusion Input بشكل كبير في عالم تصميم الالكترونيات الرقمية، حيث لجأ معظم مصممين الدارات الرقمية الى هذه التقنية وذلك لبساطتها وقدرتها على الحد من استهلاك الطاقة بسبب قلة عدد الترانزستور اللازمة لتصميم الدارة الرقمية.

تعتمد تقنية GDI على استخدام خلية بسيطة مكونة من ترانزستورين نوع NMOS و PMOS مع أربع نهايات هي:

G مدخل البوابة المشتركة للترانزستورات NMOS و PMOS.

P مدخل الترانزستور PMOS.

N مدخل الترانزستور NMOS و OUTPUT وهو مخرج مشترك للترانزستورين [20].

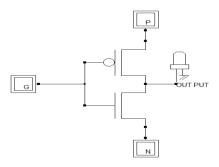

الشكل (3) يبين البنية الاساسة لخلية GDI.

الشكل (3): البنية الاساسة لخلية GDI.

تتشابه خلية GDI من حيث البنية مع الخلية الأساسية لعاكس CMOS القياسي، ولكن هناك بعض الاختلافات الرئيسية والمهمة حيث تتميز خلية GDI بأن المنبع (S) للترانزستور PMOS في غير متصل بقطب التغذية VDD وكذلك المنبع (S) للترانزستور NMOS غير متصل بقطب التغذية

يتم التحكم بعمل هذه الخلية من خلال التحكم بقيم المنافذ (G,P,N )، يبين الجدول (3) كيف يمكن التحكم بعمل خلية الـ GDI من خلال تغيير قيم المداخل.

OUT Function Ν G 0 В A'B F1 Α A'+B F2 В 1 Α 1 Α A+B OR В 0 Α A.B AND С Α A'B+AC MUX A' NOT

الجدول(3): الوظائف المنطقية لخلية GDI

#### 4- الدارة العملية:

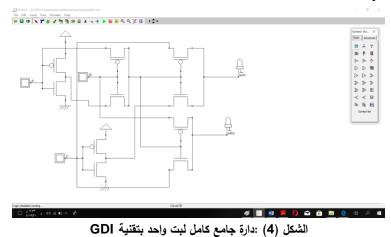

#### 4- 1 دارة الجامع الكامل لبت واحد بتقنية GDI:

ظهرت العديد من الدراسات التي اهتمت بتصميم دارة جامع كامل لبت واحد وفق تقنية GDI [11-15]. في هذه الدراسة قد اعتمدنا على الدارة المبينة بالشكل (4) حيث أنها تتميز بسهولة التصميم وبالعدد القليل من الترانزستورات التي تشكلها.

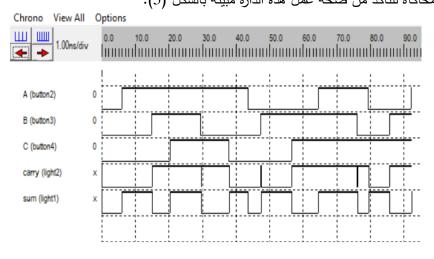

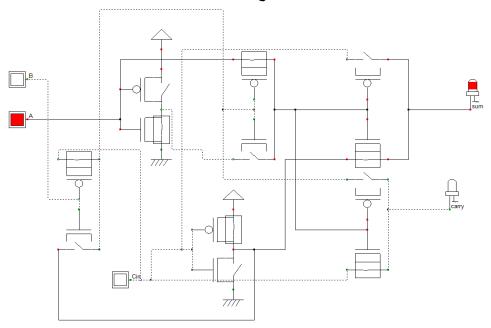

نتائج المحاكاة للتأكد من صحة عمل هذه الدارة مبينة بالشكل (5).

الشكل (5): نتائج محاكاة دارة جامع كامل لبت واحد بتقنية GDI

## 4- 2 دارة الجامع الطارح لاربع بت بتقنية GDI:

بعد أن استعرضنا بنية دارة جامع كامل لبت واحد بالاعتماد على تقنية Gate Diffusion Input بعد أن استعرضنا بنية دارة جامع طارح لاربع بت

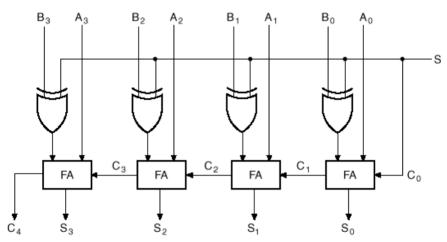

يبين الشكل (6) الدارة االتقليدية لجامع /طارح باربع بت

الشكل (6) : الدارة التقليدية لجامع /طارح باربع بت

نتألف الدارة بشكل أساسي من دارات جامع كامل لبت واحد ( FA ) و بوابات XOR مع خط تحكم ( S) من أجل التحكم بعملية الطرح والجمع حيث (A0, B0, A1, B1, A2, B2, A3, B3) هي مداخل الدارة الأساسية لاربعة بت، (S0, S1, S2, S3) هي مخارج الدارة.

#### مهمة خط التحكم هي:

عندما S=0 تقوم الدارة بعملية الجمع النظامية.

عندما S=1 تقوم الدارة بعملية الطرح وذلك عن طريق اخذ المتمم الثاني للعدد (b) وذلك من خلال اخذ المتمم الأول عن طريق بوابة ال XOR ثم إضافة للبت الأول وذلك عن طريق دارة الجامع التي تتحكم بأول بت (حيث تم وصل ال Cin بشكل مباشر مع خط التحكم S الذي قيمته في هذه الحالة تساوي الواحد المنطقي)

## 4- 3 التصميم المقترح لدارة الجامع الطارح لاربع بت بتقنية GDI:

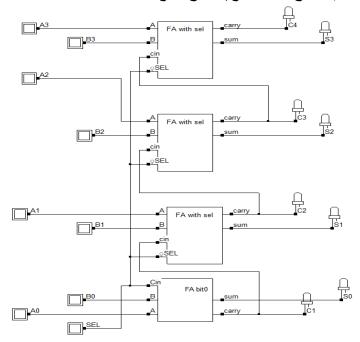

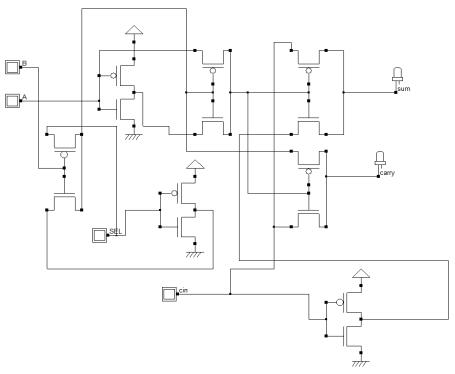

يبين الشكل (7) التصميم المقترح لدارة الجامع/ الطارح لاربع بت وفق تقنية GDI

الشكل (7) التصميم المقترح لدارة الجامع/ الطارح لاربع بت وفق تقنية GDI

الفكرة الرئيسية للتصميم المقترح تعتمد على فكرة استخدام وحدتين أساسيتين واضافة إشارة تحكم هي SEL، الوحدتان الاساسيتان هما:

وحدة الـ FA bitO : وهي مخصصة لجمع او طرح البت الأول فقط من العددين A و B وحدة الـ FA with sel : و هي مخصصة لجمع او طرح ما تبقى من بتات العددين A و B

#### 4- 3 −1 التصميم المقترح لوحدة FA bit0 :

من أجل إتمام عملية الجمع والطرح قمنا بتعديل البنية الاساسة لدارة جامع كامل لبت واحد بتقنية الاالمذكورة بالشكل (4) حيث عند عملية الطرح يجب أن يتم اخذ المتمم الأول للعدد B واضافة 1 لينتج المتمم الثنائي

يبين الشكل (8) البنية الأساسية لوحدة FA bit0

الشكل (8) البنية الأساسية لوحدة FA bit0

حيث تم استخدام المدخل CIN/SEL كمدخل تحكم ومدخل CIN بنفس الوقت:

عندما CIN/SEL=0 ستعمل هذه الوحدة كدارة جامع لبت واحد ولكن فقط من أجل البت الأول للعددين المراد جمعهما مثل الدارة المبينة بالشكل (4)

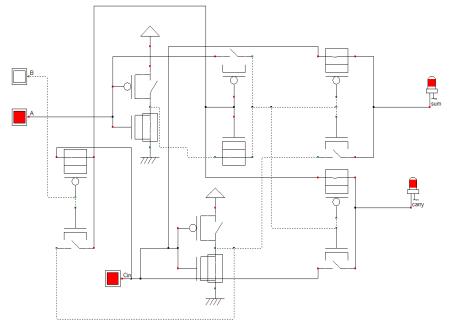

عندما CIN/SEL=1 هنا سيكون عملها كدارة طارح لبت واحد وستكون هذه الإشارة بمثابتة إشارة قيادة للوحدات الأخرى FA bit0 . يبين الشكل (7) سلوك وحدة FA bit0 من أجل:

A=1 B=0 Cin=0 حيث تعمل الدارة كدارة جامع لبت وحيد.

يبين الشكل (9) : وحدة FA bit0 كدارة جامع لبت وحيد

يبين الشكل (10) سلوك وحدة FA من أجل :A=1 B=0 Cin=0 حيث تعمل الدارة كدارة طارح لبت وحيد.

الشكل (10): وحدة FA كدارة طارح لبت وحيد.

#### 4- 3 -1 التصميم المقترح لوحدة FA with sel :

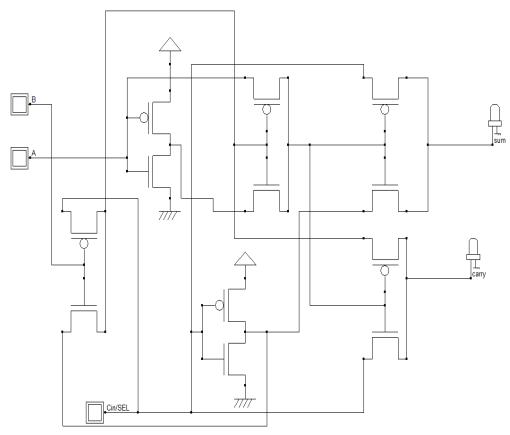

هذه الوحدة ستكون مسؤولة عن عمليات الجمع و الطرح للبتات المتبقة من العددين المراد جمعهما او طرحهما. الشكل (11) يبين البنية الداخلية لهذه الوحدة بتقنية GDI، حيث تم فصل خط الـ CIN عن خط الـ SEL عن طريق تعديل البنية وذلك بإضافة ترانزستورينNMOS, PMOS بنية الجامع الأساسية.

الشكل (11) : البنية الداخلية لوحدة FA with sel

يتم التحكم بخط ال SEL لتحديد عملية الجمع (SEL=0) أو عملية الطرح (SEL=1) وذلك من خلال المدخل الرئيسي للدارة (SEL ) كما هو مببن بالشكل (9) أما الـ CIN فهو الحمل القادم من البت الادنى

### 5- النتائج العملية و المناقشة:

#### 5-1 الدارة العملية:

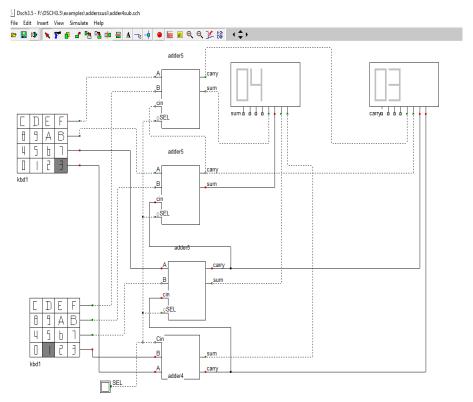

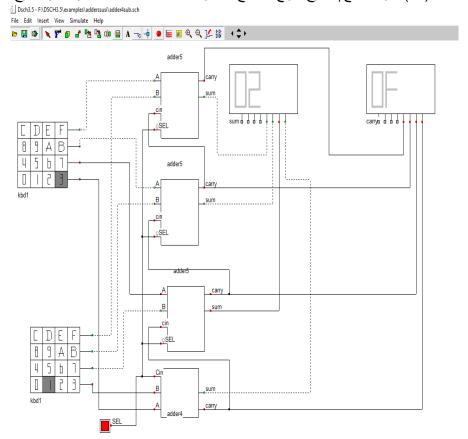

تم الاعتماد على برنامج DSCH3.5 من اجل عملية محاكاة دارة الجامع/الطارح لاربع بت بتقنية GDI يبين الشكل (12) سلوك دارة الجامع/الطارح لاربع بت مع اعتبار SEL=0

الشكل (12) دارة الجامع/الطارح لاربع بت مع اعتبار SEL=0

يبين الشكل (13) دارة الجامع/الطارح لاربع بت مع اعتبار SEL=1 حيث تعمل الدارة كدارة طارح

## الشكل (13) دارة الجامع/الطارح لاربع بت مع اعتبار 1=1 SEL من صحة عمل هذه الدارة مبينة بالشكل (14).

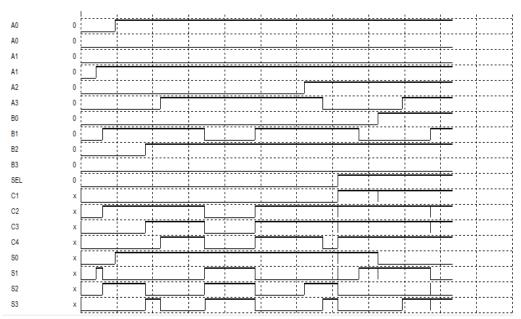

الشكل (14) : نتائج محاكاة دارة جامع/طارح لاربع بت بتقنية GDI

## 2-5 مرحلة رسم الخريطة الفيزيائية Layout:

من اجل رسم ومحاكاة الخريطة الفيزيائية Layout لهذه الدارة، تم الاعتماد على برنامج والمحاكاة السابقة . Werilog وعلى ملف الوصف البنوي بلغة Verilog من المحاكاة السابقة .

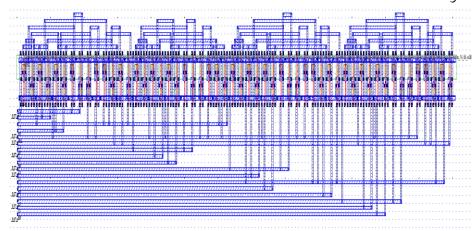

الشكل (15) يبين الخريطة الفيزيائية "layout" لوحدة FA bit0 و الشكل (16) يبين الخريطة الفيزيائية "layout" لوحدة FA with sel

الشكل (15) : الخريطة الفيزيائية لوحدة 15)

الشكل (16) : الخريطة الفيزيائية لوحدة FA with sel

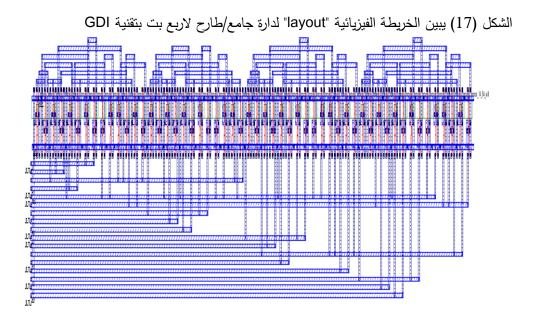

الشكل (17) : الخريطة الفيزيائية لدارة جامع/طارح لاربع بت بتقنية GDI

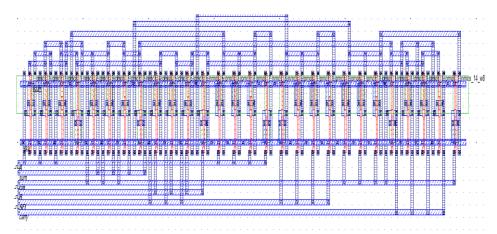

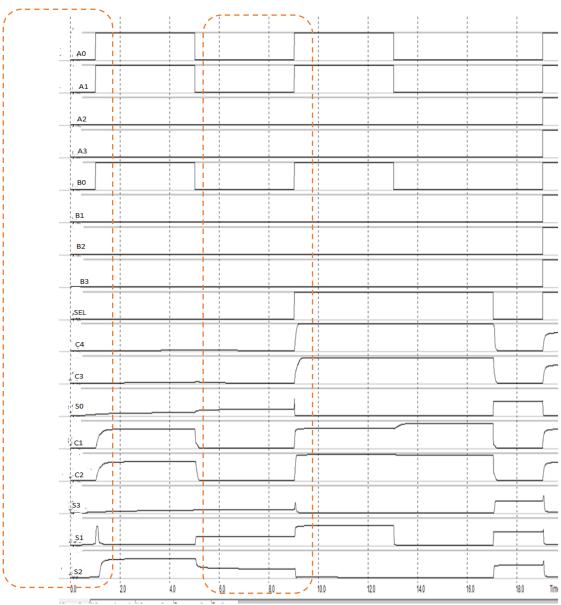

نتائج محاكاة الخريطة الفيزيائية "layout" لدارة جامع/طارح لاربع بت بتقنية GDI مبينة بالشكل (18)

الشكل (18) : نتائج محاكاة الخريطة الفيزيائية "layout" لدارة جامع/طارح لاربع بت

نلاحظ من الشكل السابق انه عندما:

وعندما SEL=1 فالعملية هي عملية طرح والناتج هو :

. C4 C3 C2 C1=1 1 1 1 و S3 S2 S1 S0=0 0 1 0 و S4 C3 C2 C1=1 1 1 1

من أجل عمليات مقارنة الأداء من حيث مساحة الرقاقة والطاقة المستهلكة لكلا الدارتين، فإن رسم الخريطة لفيزيائية Layout لدارة الجامع/الطارح لاربع بت سيتم بالاعتماد على عدة تقنيات لتكنولوجيا تصنيع الدرارات الالكترونية وهي:

65nm و 45nm وهي التقنيات التي اعتمدت عليها معظم الدراسات السابقة، وفي هذا البحث قمنا باستخدام تقنيتين جديدتين هما 32nm و كذلك 22nm .

يسمح برنامج MICROWIND 3.1 بحساب مساحة الرقاقة و الطاقة المستهلكة لكل تقنية مستخدمة حيث يتم حساب الطاقة المستهلكة من المعادلة التالية[14]:

#### P=Supply voltage (Vdd)\* Current (I)

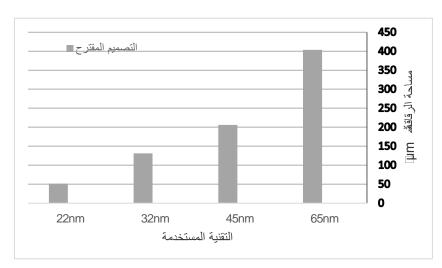

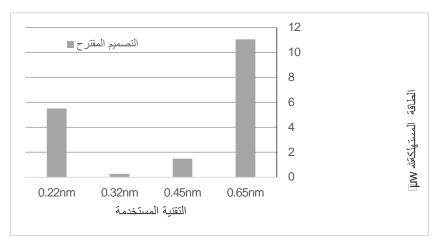

يبين الجدول (4) مقارنة مابين مساحة الرقاقة والطاقة المستهلكة لدارة الجامع/الطارح المقترحة بتقنية GDI من أجل عدة تقنيات تصنيع

الجدول(4): مساحة الرقاقة والطاقة المستهلكة

| التقنية المستخدمة (nm) | 65     | 45    | 32    | 22    |

|------------------------|--------|-------|-------|-------|

| جهد التغذية [Vdd[V     | 0.70   | 0.40  | 0.35  | 1     |

| مساحة الرقاقة (μm²)    | 403.8  | 206   | 131   | 51.5  |

| الطاقة المستهلكة (uw)  | 11.052 | 1 496 | 0.570 | 5.513 |

الشكل (19) يبين نتائج

المقارنة للتصميم المقترح لدارة جامع/طارح باربع بت من حيث مساحة الرقاقة و الشكل (20) يبين نتائج المقارنة من حيث الطاقة المستهلكة و ذلك من أجل التقنيات: 32nm ، 45nm ، 65nm .

الشكل (19): نتائج المقارنة من حيث ساحة الرقاقة للتقنيات المستخدمة

الشكل (20): نتائج المقارنة من حيث الطاقة المستهلكة للتقنيات المستخدمة

كما هو واضح من نتائج المقارنة فإن التقنية 22nm هي الأفضل من حيث المساحة على الرقاقة ولكن من حيث الطاقة المستهلكة فهي تستهلك طاقة اكثر وذلك بسبب جهد التغذية لهذه التقنية وهو Vdd=1V

#### 6-الاستنتاجات والتوصيات:

في هذا البحث تم تصميصم وتحليل أداء دارة جامع/طارح لاربع بت بالعتماد علىبتقنية GDI.

وتمت عملية رسم و دراسة الخريطة الفيزيائية للدارة بالاعتماد على عدة تقنيات تصنيع. وبمقارنة نتائج المحاكاة نلاحظ أن دارة الجامع/الطارح المقترحة تعمل بكفاءة عالية وهي جيدة من حيث المساحة على الرقاقة ومن حيث الطاقة المستهلكة مهما كانت التقنية المستخدمة في التصنيع ويعود ذلك إلى العدد القليل من الترانزستورات المستخدم في تصمصم الدارة وبنسبة توفير في المساحة على الشريحة حيث مساحة الدارة وينسبة توفير في المساحة على الشريحة حيث مساحة الدارة من أجل التقنية الى تقنية 22nm وانخفضت الى51.5μm²

#### 7- المراجع العلمية

- [1] Jan, M. Rabaey, Chandrakasan Anantha, and Nikolic Borivoje. "Digital Integrated Circuits—A Design Perspective." (2003).

- [2] Pucknell, Douglas A., and Kamran Eshraghian. Basic VLSI design: systems and circuits. Englewood Cliffs, New Jersey,, USA: Prentice Hall, 1988..

- [3] Bui, Hung Tien, Yuke Wang, and Yingtao Jiang. "Design and analysis of low-power 10-transistor full adders using novel XOR-XNOR gates." IEEE Transactions on Circuits and Systems II: Analog and Digital Signal Processing 49, no. 1 (2002): 25-30.

- [4] Jiang, Yingtao, Abdulkarim Al-Sheraidah, Yuke Wang, Edwin Sha, and Jin-Gyun Chung. "A novel multiplexer-based low-power full adder." IEEE Transactions on Circuits and Systems II: Express Briefs 51, no. 7 (2004): 345-348.

- [5] Lin, Jin-Fa, Yin-Tsung Hwang, Ming-Hwa Sheu, and Cheng-Che Ho. "A novel high-speed and energy efficient 10-transistor full adder design." IEEE Transactions on Circuits and Systems I: Regular Papers 54, no. 5 (2007): 1050-1059.

- [6] Wang, Dan, Maofeng Yang, Wu Cheng, Xuguang Guan, Zhangming Zhu, and Yintang Yang. "Novel low power full adder cells in 180nm CMOS technology." In 2009 4th IEEE Conference on Industrial Electronics and Applications, pp. 430-433. IEEE, 2009.

- [7] Uma, R. "4-Bit Fast Adder Design: Topology and Layout with Self-Resetting Logic for Low Power VLSI Circuits"." International Journal of Advanced Engineering Sciences and Technology 7, no. 2 (2011): 197-205.

- [8] Veeramachaneni, Sreehari, and M. B. Srinivas. "New improved 1-bit full adder cells." In 2008 Canadian Conference on Electrical and Computer Engineering, pp. 000735-000738. IEEE, 2008.

- [9] Chen, Chuen-Yau, and Yung-Pei Chou. "Novel low-power 1-bit full adder design." In 2009 9th International Symposium on Communications and Information Technology, pp. 1348-1349. IEEE, 2009.

- [10] Khatibzadeh, Amir Ali, and Kaamran Raahemifar. "A 14-transistor low power high-speed full adder cell." In CCECE 2003-Canadian Conference on Electrical and Computer Engineering. Toward a Caring and Humane Technology (Cat. No. 03CH37436), vol. 1, pp. 163-166. IEEE, 2003.

- [11] Lakshmaiah, Dayadi, M. V. Subramanyam, and K. Sathya Prasad. "A Novel Design of Low-Power 1-Bit CMOS Full-Adder Cell Using XNOR and MUX." INTERNATIONAL JOURNAL OF MANAGEMENT & INFORMATION TECHNOLOGY 7, no. 3 (2013): 1155-1165.

- [12] Reddy, Karthik G. "Low power-area designs of 1bit Full adder in cadence virtuoso platform." International Journal of VLSI Design & Communication Systems 4, no. 4 (2013): 55.

- [13] Uma, R., and P. Dhavachelvan. "Modified gate diffusion input technique: a new technique for enhancing performance in full adder circuits." Procedia Technology 6 (2012): 74-81.

- [14] Sreelatha, P., P. Koti Lakshmi, and Rameshwar Rao. "Performance analysis of 1-bit full adder using different design techniques." In 2017 2nd IEEE International Conference on Recent Trends in Electronics, Information & Communication Technology (RTEICT), pp. 2262-2266. IEEE, 2017.

- [15]صالح، سوزي "تحليل و تقييم أداء دارة جامع كامل لبت واحد مصنعة وفق تقنية Static CMOS و تقنية GDI و تقنية GDI و أثر تغير التكنولوجيا المستخدمة في التصنيع على الأداء" مجلة جامعة طرطوس للبحوث و الدراسات التعليمية ، سلسلة العلوم الهندسية المجلد (الثالث) العدد (الرابع) 2019

- [16] SUSHMITA, D. Veena, et al. "Design of High Performance Full Subtractor using FinFET". International Journal of Engineering Science, 2017, 5885.

- [17] DHAR, Krishnendu; CHATTERJEE, Aanan; CHATTERJEE, Sayan. Design of an energy efficient, high speed, low power full subtractor using GDI technique. In: Proceedings of the 2014 IEEE Students' Technology Symposium. IEEE, 2014. p. 199-204.

- [18] Sandip B. Rahanel Tushar T. Korade "Gate Diffusion Input Full Subtractor Circuit using 130nm Technology". IJSRD International Journal for Scientific Research & Development Vol. 5, Issue 04, 2017

- [19] SINGH, Kamal Jeet; MEHRA, Rajesh. "Design &Analysis of Full Subtractor using 10T at 45nm Technology". International Journal Of Engineering Trends and Technology (IJETT), 2016, 35.9: 449.

- [20] VERMA, Ranjeeta; MEHRA, Rajesh."CMOS based design simulation of adder/subtractor using different foundries. International Journal of Science and Engineering, 2013, 2.1: 28-34.

- [21] Sarkar, Sudeshna, Monika Jain, Arpita Saha, and Amit Rathi. "Gate Diffusion Input: A technique for fast digital circuits (implemented on 180 nm technology)." IOSR Journal of VLSI and Signal Processing (IOSR-JVSP) 4, no. 2 (2014): 49-53.