مجلة جامعة طرطوس للبحوث والدراسات العلمية \_ سلسلة العلوم الهندسية المجلد (5) العدد(5) 2021

Tartous University Journal for Research and Scientific Studies - engineering Sciences Series Vol. (5) No. (5) 2021

# Design and simulation of 1 bit arithmetic logic unit circuit using quantum dot cellular automation technology

Eng. Yana Ghanim\*

(Received 25 /3 / 2021 . Accepted 27 / 6 / 2021)

## □ ABSTRACT □

The term "nanoelectronics" refers to the incorporation of nanotechnology into electronic components and this term covers a wide range of materials and devices that the nanoscales feature collects them(1-100)nm, as interactions at this level are subject to the laws of quantum mechanics.

The example of elements at this level include: molecular electronics, semiconductors, nanotubes and quantum dots.

In this research we have built a design of 1-bit arithmetic logic unit circuit using quantum dot technology, one of the candidate technologies to replace the CMOS techniques that is used in building the widest number of existing electronics devices.

**Keywords**: Nanotechnologies -Quantum dots-Arithmetic logic unit -Quantum computing.

53

<sup>\*</sup>Electronic engineering master degree-Department of computer and electronic engineering- Faculty of information and communication technology- Tartus University, Syria.

مجلة جامعة طرطوس للبحوث والدراسات العلمية \_ سلسلة العلوم الهندسية المجلد (5) العدد (5) العدد (5) مجلة جامعة طرطوس للبحوث والدراسات العلمية \_ سلسلة العلوم الهندسية المجلد (5) العدد (5) ا

# "تصميم ومحاكاة دارة وحدة حساب ومنطق ذات بت واحد باستخدام تقنية أتمتة خلايا النقاط الكمومية"

م. يانا غانم \*

(تاريخ الإيداع 25/ 3 /2021 . قُبِل للنشر في 27 /6 /2021 )

# 🗖 ملخّص 🗖

يشير مصطلح الإلكترونيات النانوية إلى دمج تقنية النانو في المكونات الإلكترونية ويغطي هذا المصطلح مجموعة واسعة من المواد والأجهزة التي تجمعها سمة المقياس النانوي (1-100) نانومتر، حيث إن التفاعلات في هذا المستوى لا تخضع لقوانين الفيزياء التقليدية بل تكون قوانين ميكانيك الكم هي السائدة.

نتضمن الأمثلة على العناصر في هذا المستوى: الإلكترونيات الجزيئية وأشباه الموصلات الهجينة والأنابيب النانوية والنقاط الكمومية.

قمنا في هذا البحث ببناء تصميم لوحدة الحساب والمنطق بالاعتماد على تقنية أتمتة خلايا النقاط الكمومية، وهي أحد تقنيات الإلكترونيات النانوية الحديثة المرشحة للحلول محل تقنيات ال CMOS المستخدمة في تصنيع الطيف الأوسع من الأجهزة الإلكترونية الحالية.

الكلمات المفتاحية: تكنولوجيا النانو - النقاط الكمومية -وحدة الحساب والمنطق -الحوسبة الكمومية.

<sup>\*</sup>ماجستير في هندسة تكنولوجيا الإلكترونيات-قسم هندسة النظم الحاسوبية والإلكترونية- كلية هندسة تكنولوجيا المعلومات والاتصالات-جامعة طرطوس - سورية.

## 1-مقدمة:

تحسن تصنيع الدارات المتكاملة باستخدام تقنية ال CMOS خلال النصف الثاني من القرن العشرين وحتى الآن نتيجة لتصغير حجم الترانستورات مما قاد إلى تخفيض استهلاك الطاقة وتحسين سرعة الدارات المتكاملة، وعلى الرغم من ذلك فقد حرّضت القيود الفيزيائية لتقنية ال CMOS الدراسات بهدف البحث عن بدائل لهذه التقنية.

تعد تقنية أتمتة خلايا النقاط الكمومية أحد أفضل الخيارات المتاحة نتيجة لترددات عملها العالي، وحجمها الصغير واستهلاكها المنخفض للطاقة، وهي أحد أهم التقنيات النانوية المناسبة للأنظمة الرقمية، ويعتمد مبدأ عملها على قوى نتافر كولون بين الإلكترونات[1][2][3].

# 2- أهداف البحث:

تتاولت الدراسات السابقة تصاميم مختلفة لوحدة الحساب والمنطق من حيث عدد العمليات ونوعها وعدد البيتات، تضمّن النموذج في الدراسة [4] ثلاث وظائف اثنتان حسابيتان وهي نصف الجامع ونصف الطارح ووظيفة منطقية واحدة وهي وظيفة and في حين تم في هذه الدراسة [5] فصل وحدتي الحساب والمنطق عن بعضهما واستخدام ناخبين 4X1 لاختيار الوظيفة الحسابية أو المنطقية المطلوبة ومن ثم ناخب 2X1 للاختيار بين خرج وحدة الحساب أو خرج وحدة المنطق وكان عدد العمليات الحسابية والمنطقية غير المكررة التي ينجزها هذا التصميم 10، في حين تناولت الدراسة [6] تصميم وحدة حساب ومنطق ب8 بيتات، ويتلخّص هدفنا من هذا البحث في:

- بناء وحدة الحساب والمنطق ذات بت واحد باستخدام تقنية أتمتة خلايا النقاط الكمومية تقوم بالإضافة إلى العمليات المنطقية الأساسية(and,xor,or,not)، بعمليات الجمع والطرح الكاملين (مع حمل ، مع استعارة)

- العمل على أمثلة التصميم قدر الإمكان.

# 3- طرائق البحث ومواده:

#### 1-3 النقاط الكمومية

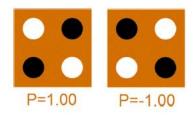

ظهرت هذه التقنية عام 1993، وتتكون كل خلية كمومية من أربع نقاط كمومية والكترونين، وكل نقطة هي جزيئة نانوية أو كريستالية (مصنوعة من المواد نصف الناقلة كالسيليكون وسيلينيد الكادميوم) [7]، ويحدد تموضع الالكترونين الحالة المنطقية "0"، ويمثل الاستقطاب p=1 الحالة المنطقية "1"، كما هو موضّح في الشكل(1).

الشكل(1): استقطابي الخلية الموافقين للحالتين المنطقيتين "0"و "1"

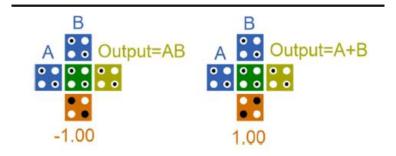

تتضمن الوظائف الأساسية في أتمتة الخلايا الكمومية وظيفة الأكثرية (majority)[8] الشكل (2)، ووظيفة النفي[9] الشكل(3)، تستخدم وظيفة الأكثرية للحصول على وظيفتي and و r بتثبيت أحد المداخل على القيمة 0 أو 1 على التوالي الشكل(4).

الشكل(2): بوابة الأكثرية (majority) بثلاث مداخل

الشكل(3): بوابة النفي

الشكل(4): الحصول على وظيفتى and, or باستخدام بوابة

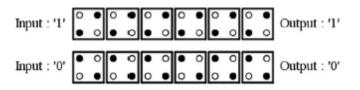

يمكن الحصول على السلك في تقنية أتمتة الخلايا الكمومية الشكل (5) عن طريق تموضع الخلايا الكمومية بجوار بعضها بعض [10]، فعندما نطبق قيمة على خلية الدخل تنتشر المعلومة الثنائية منها إلى الخلية المجاورة لخلية الدخل ومنها إلى الخلية المجاورة لها وهكذا [9].

الشكل(5): السلك في تقنية أتمتة النقاط الكمومية

# 3-2 المناطق الزمنية في أتمتة الخلايا الكمومية

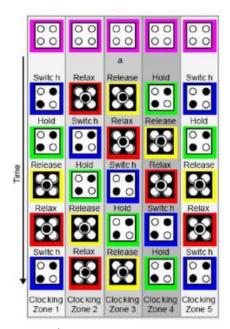

تعد الساعة أحد المتطلبات الأساسية لعمل خلايا QCA وهي مطلوبة للمزامنة والتحكم بتدفق المعلومات عبر أسلاك QCA، حيث يمكن أن نحقق انتشار الإشارة بالشكل المطلوب عن طريق التحكم بالحاجز الكمومي للخلايا في سلك QCA [4].

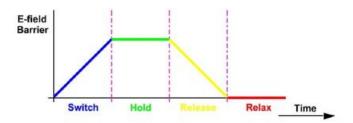

توجد أربع مناطق زمنية في تقنية أتمتة الخلايا الكمومية تتأخر كل منها عن سابقتها بمقدار ربع طور (90°):

- 1. منطقة التبديل(switch): ترتفع الحواجز الكمومية للخلية خلال هذه المرحلة بشكل تدريجي، وبذلك تتأثر الإلكترونات ضمن الخلية بالخلايا المجاورة التي تكون في مرحلة التشغيل(نتيجة لقوى تنافر كولون).

- 2. منطقة التشغيل(hold): تكون حواجز الطاقة في هذه المرحلة عالية ومستقرة بحيث تؤثر الإلكترونات في الكترونات الخلايا المجاورة بقوى كولون.

- 3. منطقة الإطلاق(release): تتخفض حواجز الطاقة وتفقد الخلية استقطابها تدريجياً.

- 4. منطقة الراحة(relax): تصبح الحواجز الكمومية معدومة، والخلية غير مستقطبة وغير قادرة على نقل الاستقطاب(المعلومة) إلى الخلايا المجاورة.

يوضّح الشكل(6) كيفية انتشار المعلومة عبر عدة خلايا كمومية متجاورة، ويوضّح الشكل(7) حاجز الطاقة للخلية الموافق لكل مرحلة.

الشكل(6): المناطق الزمنية للساعة المستخدمة في أتمتة الخلايا الكمومية

الشكل(7): حاجز طاقة الخلية الموافق لكل طور من أطوار الساعة

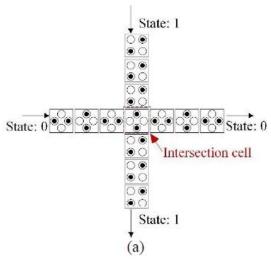

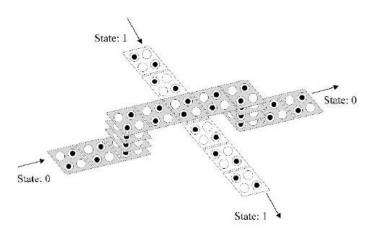

# 3-3 الجسور (Crossovers)

عند تصميم دارات QCA يجب منع حدوث تقاطع بين الأسلاك وتداخل في الإشارات حيث يسمح في تصميم QCA بثلاثة أنواع من الجسور لمنع التقاطع هي[12,11]:

- a) الجسر وحيد المستوى (coplanar crossover): يستخدم طبقة وحيدة من الخلايا لكنه يتضمن استخدام نوعين من الخلايا في هذه الطبقة (تسمى منتظمة ومدوّرة )، ويوضّح الشكل (8) الجسر وحيد المستوى، حيث الفارق في الزاوية بين الخلايا المنتظمة والمدوّرة بمقدار °45 يسمح بانتقال الإشارتين في السلكين دون حدوث أي تداخل .

- b) الجسر متعدد الطبقات(multilayer crossover): يستخدم عدة طبقات من الخلايا كما في الطبقات المعدنية في الدارات المتكاملة التقليدية، ويوضّح الشكل(9) الجسر متعدد المستويات.

- (c) الجسر المنطقي(logical crossover): هذه الطريقة هي أكثر موثوقية وتسامح للأخطاء من الطريقتين السابقتين، ويعتمد مبدأ عملها على التزامن المستخدم في أتمتة خلايا النقاط الكمومية، إذ أنه حتى تؤثر الخلية في الخلايا المجاورة يجب أن تكون في مرحلة التشغيل، وحتى تتأثر الخلية بالخلايا المجاورة يجب أن تكون في مرحلة التبديل، ويوضّح الشكل(10) الجسر المنطقي حيث تنتشر الإشارة في السلك الأول (المنطقة الزمنية الأولى) بشكل مستقل عن الإشارة في السلك الثاني(المنطقة الزمنية الثالثة)، ويمكن استخدم أي منطقتين زمنيتين غير متتاليتين في بناء الجسر المنطقي.

الشكل(8): الجسر وحيد المستوى في تقنية أتمتة النقاط الكمومية

الشكل(9): الجسر متعدد الطبقات في تقنية أتمتة النقاط الكمومية

الشكل(10): الجسر المنطقي في تقنية أتمتة النقاط الكمومية

#### 4-3 محاكى QCADesigner

محاكي QCADesigner : هو أداة أوجدت خصيصاً لتصميم مخططات أتمتة خلايا النقاط الكمومية ودراسة أدائها واستخلاص خرجها وتسمح هذه الأداة بثلاثة أنواع مختلفة من المحاكاة للحصول على نتائج دقيقة وموثوقة.

تم تطوير هذه الأداة للمرة الأولى في مختبرات جامعة Calgary في كندا وما زالت في طور التعديل والتحسين حتى يومنا هذا لاستخدامها في دراسة خصائص إضافية لتصاميم QCA كاستهلاك الطاقة وغيرها، ويمكن تحميل أحدث النسخ من هذا المحاكي QCADesigner2.0.3 من موقع جامعة British Coloumbia].

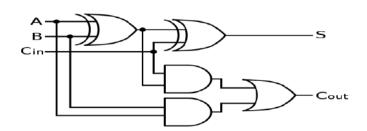

## 3-5 التصميم الكمومي لدارة وحدة الحساب والمنطق

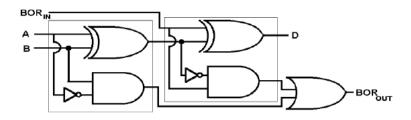

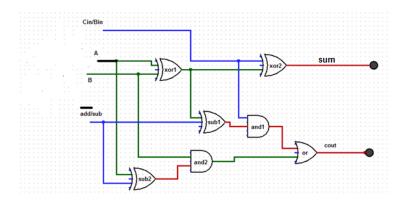

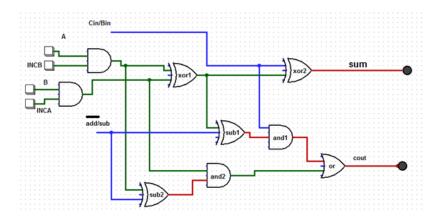

تتضمن وحدة الحساب والمنطق وظيفتي الجمع والطرح الكاملين[15]، ويوضّح الشكل (11) دارة الجامع الكامل[16]، ويوضّح الشكل (12) دارة الطارح الكامل، نلاحظ أن الوحدتين متشابهتين باستثناء عمليتي not إضافيتين على مدخلي بوابتي and لدارة الطارح الكامل، ولدمج الوحدتين معاً نستخدم بوابتي xor على مدخلي بوابتي dad الهارة الشارة الهوابتان إشارة الهارة الهارة أعلى أحد مدخلي بوابة xor بحيث عندما قيمة الإشارة ويمر الدخل الثاني لبوابة xor كما هو إلى الخرج (الجامع الكامل)، وعندما قيمة الإشارة 1 يتم عكس قيمة الدخل الثاني لبوابة xor (الطارح الكامل)، وتصبح الدارة الكلية كما هو موضّح في الشكل (13).

الشكل (11):دارة الجامع الكامل

الشكل(12): دارة الطارح الكامل

الشكل(13): دارة الجامع الطارح الكامل

وللقيام ببعض العمليات على بت واحد سنضيف بوابتي and على الدخل كما هو موضّح في الشكل(14).

الشكل(14): دارة الجامع الطارح الكامل بعد إضافة بوابتي تحكم على الدخل

بالنسبة للعمليات المنطقية فإن العمليات على بيتين (and,or,xor) والعكس لبت واحد متضمنة ضمن دارة الجامع الطارح لذلك سنقوم بدمج وحدتي الحساب والمنطق معاً لتجنب تكرار هذه الوظائف (خطوة نحو أمثلة التصميم)، ووصل خرج الجامع الطارح وبقية الوظائف إلى مداخل الناخب الخمسة.

إن الوظائف الأساسية المستخدمة في بناء التصميم الكمومي لوحدة الحساب والمنطق هي and,or,xor بالإضافة إلى وظيفة الانتخاب، بالنسبة لوظيفتي ال or و and و or يمكن الحصول عليهما باستخدام وظيفة majority كما سبق وذكرنا، أما بالنسبة لبوابة xor وقع اختيارنا على الدراسة [17] والتصميم فيها مناسب من حيث عدد الخلايا والتأخير واتجاهات المداخل والمخرج (الاتجاهات المناسبة تساعدنا في التقليل من استخدام الأسلاك)، أمّا بالنسبة للناخب أجرينا أيضاً بحثاً في الدراسات السابقة [21,20,19,18] ووقع اختيارنا على التصميم[21] (الأفضل من حيث عدد الخلايا والتأخير).

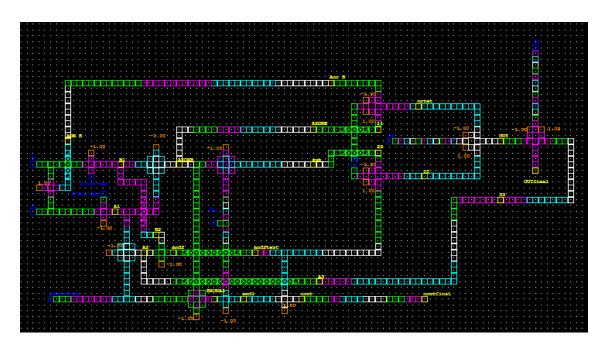

يوضّح الشكل (15) التصميم الكمومي الناتج لوحدة الحساب والمنطق.

الشكل (15): التصميم الكمومي المقترح لدارة وحدة الحساب والمنطق

يوضّح الجدول (1) الوظائف الحسابية التي يستطيع تصميمنا المقترح إنجازها بالحالة العامة (بدون تصغير أحد المدخلين أو تثبيت مدخل الحمل والاستعارة)

الجدول (1):جدول إشارات التحكم والعمليات الموافقة لدارة الجامع/الطارح

|     |            | •    |      | • ,     |         |

|-----|------------|------|------|---------|---------|

| Num | Addnot/sub | INCA | INCB | Cin/bin | out     |

| 1   | 0          | 1    | 1    | cin     | A+B+cin |

| 2   | 1          | 1    | 1    | cin     | A-B-cin |

يمكن تصفير A بجعل الإشارة INCB مساوية لل 0 كما يمكن تصفير B بجعل الإشارة INCA مساوية لل0.

ويوضّح الجدولين التاليين جدولي الحقيقة الموافقين لهاتين العمليتين.

الجدول (2): جدول الحقيقة المنطقى الموافق للعملية الحسابية A+B+cin للتصميم المقترح

| Addnot/sub | INCA | INCB | Α | В | Cin/bin | XOR1 | XOR2 | And1 | And2 | or |

|------------|------|------|---|---|---------|------|------|------|------|----|

| 0          | 1    | 1    | 0 | 0 | 0       | 0    | 0    | 0    | 0    | 0  |

| 0          | 1    | 1    | 0 | 0 | 1       | 0    | 1    | 0    | 0    | 0  |

| 0          | 1    | 1    | 0 | 1 | 0       | 1    | 1    | 0    | 0    | 0  |

| 0          | 1    | 1    | 0 | 1 | 1       | 1    | 0    | 1    | 0    | 1  |

| 0          | 1    | 1    | 1 | 0 | 0       | 1    | 1    | 0    | 0    | 0  |

| 0          | 1    | 1    | 1 | 0 | 1       | 1    | 0    | 1    | 0    | 1  |

| 0          | 1    | 1    | 1 | 1 | 0       | 0    | 0    | 0    | 1    | 1  |

| 0          | 1    | 1    | 1 | 1 | 1       | 0    | 1    | 0    | 1    | 1  |

الجدول (3): جدول الحقيقة المنطقي الموافق للعملية الحسابية A-B-Cin للتصميم المقترح

| Addnot/sub | INCA | INCB | Α | В | Cin/bin | XOR1 | XOR2 | And1 | And2 | or |

|------------|------|------|---|---|---------|------|------|------|------|----|

| 1          | 1    | 1    | 0 | 0 | 0       | 0    | 0    | 0    | 0    | 0  |

| 1          | 1    | 1    | 0 | 0 | 1       | 0    | 1    | 1    | 0    | 1  |

| 1          | 1    | 1    | 0 | 1 | 0       | 1    | 1    | 0    | 1    | 1  |

| 1          | 1    | 1    | 0 | 1 | 1       | 1    | 0    | 0    | 1    | 1  |

| 1          | 1    | 1    | 1 | 0 | 0       | 1    | 1    | 0    | 0    | 0  |

| 1          | 1    | 1    | 1 | 0 | 1       | 1    | 0    | 0    | 0    | 0  |

| 1          | 1    | 1    | 1 | 1 | 0       | 0    | 0    | 0    | 0    | 0  |

| 1          | 1    | 1    | 1 | 1 | 1       | 0    | 1    | 1    | 0    | 1  |

# 4- النتائج والمناقشة:

لمحاكاة التصميم واختبار صحة الخرج سنقوم في المرحلة الأولى باختبار كل وظيفة حسابية أو منطقية بعد تثبيت قيمة خطوط الانتخاب الثلاثة S2S1S0 على القيمة المطلوبة لانتخاب الوظيفة المطلوبة، وفي المرحلة الثانية سنقوم بتغيير قيمة خطوط الانتخاب في كل نبضة ساعة والتحقق من الوظيفة الحسابية أو المنطقية الموافقة وذلك للتأكد من عدم ثبات الناخب على نتيجة وظيفة حسابية أو منطقية معينة، ويوضت الجدول التالي قيمة خط الانتخاب الموافقة لكل عملية من العمليات الحسابية أو المنطقية.

الجدول (4): قيمة خطوط الانتخاب لانتخاب كل من العمليات الحسابية أو المنطقية

| رقم العملية | $S_0$ | $S_1$ | $S_2$ | out                                            |

|-------------|-------|-------|-------|------------------------------------------------|

| 1           | 0     | 1     | 0     | خرج عمليات الجمع والطرح                        |

|             |       |       |       | خرج عمليات الجمع والطرح الموضّحة في الجدول (1) |

| 2           | 1     | 0     | 0     | $A \otimes B$                                  |

| 3           | 1     | 1     | 0     | AandB                                          |

| 4           | 0     | 0     | 0     | AorB                                           |

| 5           | х     | х     | 1     | Ā                                              |

#### 1-4 محاكاة العملية A+B+Cin

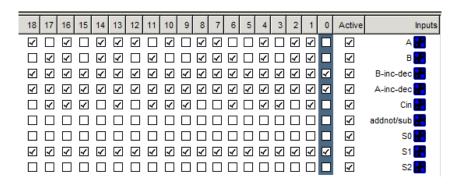

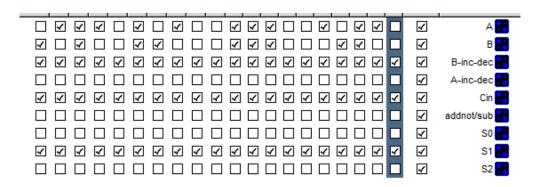

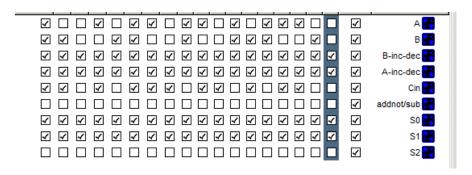

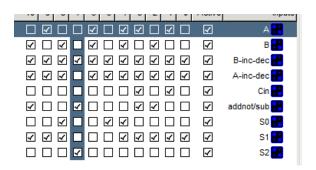

لكي نحصل على هذه العملية يجب أن تكون إشارات التحكم كما في الحالة (1) في جدول إشارات التحكم لدارة الجامع الطارح، وينبغي أن تكون إشارات الانتخاب كما في الحالة (1) لجدول إشارات الانتخاب، وعليه قمنا بتحديد إشارات المداخل على المحاكى كما في الشكل (16).

الشكل(16): قيم المداخل واشارات التحكم لدارة وحدة الحساب والمنطق لاختبار العملية A+B+Cin

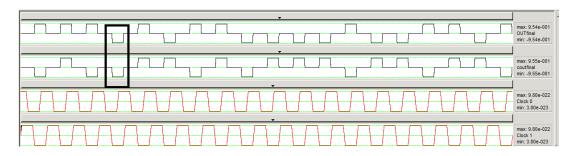

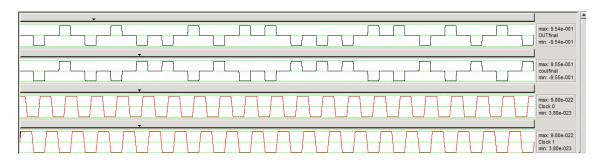

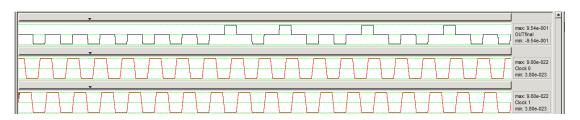

وبإجراء المحاكاة كانت النتيجة كما في الشكل (17)، حيث outfinal هي إشارة خرج الناخب وهي إشارة الخرج النهائي لوحدة الحساب والمنطق، والإشارة الثانية coutfinal هي إشارة الحمل و التأخير لكل من الإشارتين 3.25.

الشكل(17):نتيجة محاكاة دارة الحساب والمنطق الختبار العملية A+B+Cin

#### 2-4 محاكاة العملية A-B-Cin

لكي نحصل على هذه العملية يجب أن تكون إشارات التحكم كما في الحالة (2) في جدول إشارات التحكم لدارة الجامع الطارح وينبغي أن تكون إشارات الانتخاب كما في الحالة (1) لجدول إشارات الانتخاب، وعليه قمنا بتحديد إشارات المداخل على المحاكي كما في الشكل (18)

الشكل(18): قيم المداخل واشارات التحكم لدارة وحدة الحساب والمنطق لاختبار العملية A-B-Cin

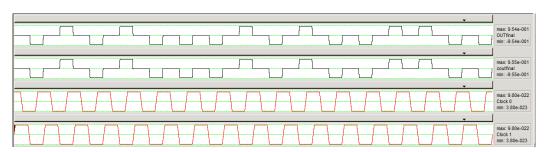

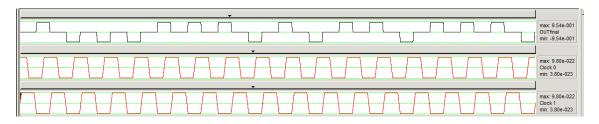

وبإجراء المحاكاة كانت النتيجة كما في الشكل (19)، حيث outfinal هي إشارة خرج الناخب وهي إشارة الخرج النهائي لوحدة الحساب والمنطق، والإشارة الثانية coutfinal هي إشارة الاستعارة و التأخير للإشارتين 3.25

الشكل(19):نتيجة محاكاة دارة وحدة الحساب والمنطق لاختبار العملية A-B-Cin

# 4-3 محاكاة عملية الزيادة للدخل A ( ++A):

لكي نحصل على هذه العملية الحسابية يجب أن تكون إشارات التحكم كما في الحالة (1) في جدول إشارات التحكم لدارة الجامع الطارح مع تثبيت المدخل R وتثبيت قيمة Oin على القيمة وينبغي أن تكون إشارات الانتخاب كما في الحالة (1) لجدول إشارات الانتخاب ، وعليه قمنا بتحديد إشارات الدخل على المحاكى كما في الشكل (20)

الشكل(20): قيم المداخل واشارات التحكم لدارة وحدة الحساب والمنطق الختبار العملية ++A

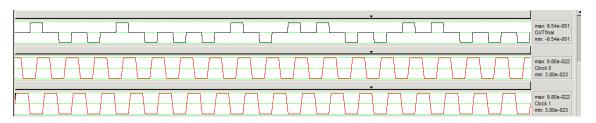

وبإجراء المحاكاة كانت النتيجة كما في الشكل (21)، حيث outfinal هي إشارة خرج الناخب وهي إشارة الخرج الناهائي لوحدة الحساب والمنطق، والإشارة الثانية coutfinal هي إشارة الحمل الناتجة عن زيادة A و التأخير للإشارتين 3.25.

الشكل(21):نتيجة محاكاة دارة وحدة الحساب والمنطق لاختبار العملية ++A

# 4-4 محاكاة عملية إنقاص الدخل A (--A):

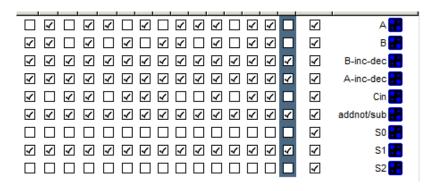

لكي نحصل على هذه العملية يجب أن تكون إشارات التحكم كما في الحالة (2) في جدول إشارات التحكم لدارة الجامع الطارح مع تثبيت المدخل INCA على القيمة 0 لإلغاء المدخل B وتثبيت قيمة المدخل على القيمة 1 وينبغي أن تكون إشارات الانتخاب كما في الحالة (1) لجدول إشارات الانتخاب، وعليه قمنا بتحديد إشارات المداخل على المحاكى كما في الشكل (22)

|          | ✓        | A 🔀          |

|----------|----------|--------------|

|          | ✓        | В 🔀          |

|          | 4        | B-inc-dec 🔀  |

| <b>_</b> | <b>√</b> | A-inc-dec 🔀  |

|          | ✓        | Cin 🔀        |

|          | ✓        | addnot/sub 🎛 |

|          | ✓        | S0 🔀         |

|          | 4        | S1 🔀         |

|          | 4        | S2 🔐         |

الشكل(22): قيم المداخل واشارات التحكم لدارة وحدة الحساب والمنطق لاختبار العملية -- ٨

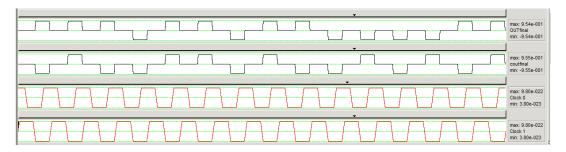

وبإجراء المحاكاة كانت النتيجة كما في الشكل (23)، حيث outfinal هي إشارة خرج الناخب وهي إشارة الخرج النهائي لوحدة الحساب والمنطق، والإشارة الثانية coutfinal هي إشارة الاستعارة الناتجة عن إنقاص A و التأخير للإشارتين 3.25.

الشكل(23):نتيجة محاكاة دارة وحدة الحساب والمنطق لاختبار العملية — ٨

#### $A \otimes B$ محاكاة العملية $A \otimes B$

لكي نحصل على هذه العملية يجب أن تكون إشارات التحكم كما في الحالة (2) لجدول إشارات الانتخاب، وعليه قمنا بتحديد إشارات المداخل على المحاكي كما في الشكل (24).

|                                              | .            |     | -   -                           |              |                                     |            |   |              |

|----------------------------------------------|--------------|-----|---------------------------------|--------------|-------------------------------------|------------|---|--------------|

|                                              |              |     |                                 | $\square$    | $ \mathbf{A}  \square  \mathbf{A} $ | <b>√</b> □ | < | A 🔐          |

| $ \mathbf{A}  \square  \mathbf{A}  \square $ |              |     |                                 |              |                                     |            | < | В 🚼          |

| $\checkmark$ $\checkmark$ $\checkmark$       | $\checkmark$ |     | $\checkmark$                    | $\checkmark$ | $\checkmark$                        | <b>√</b>   | < | B-inc-dec 🎇  |

| $\checkmark$                                 | $\checkmark$ |     | $\checkmark$                    | $\checkmark$ | $\checkmark$                        | <b>√</b>   | < | A-inc-dec 🎇  |

|                                              |              |     | $\ \square \ \square \ \square$ |              |                                     |            | < | Cin 🎇        |

|                                              |              |     | $\ \square \ \square \ \square$ |              |                                     |            | ✓ | addnot/sub 🎛 |

| $\checkmark$                                 | $\checkmark$ | 7 4 | $\checkmark$                    | $\checkmark$ | $\checkmark$                        | <b>√</b>   | ✓ | S0 🔀         |

|                                              |              |     | $\ \square \ \square \ \square$ |              |                                     |            | < | S1 🔀         |

|                                              |              |     | $\ \square \ \square \ \square$ |              |                                     |            | ✓ | S2 🚼         |

الشكل(24): قيم المداخل وإشارات التحكم لدارة وحدة الحساب والمنطق لاختبار العملية A XOR B

وبإجراء المحاكاة كانت النتيجة كما في الشكل (25)، حيث outfinal هي إشارة خرج الناخب وهي  $A \otimes B$  ، و التأخير للإشارة 3.25.

الشكل(25):نتيجة محاكاة دارة وحدة الحساب والمنطق لاختبار العملية A XOR B

#### 4-6 محاكاة العملية A.B:

لكي نحصل على هذه العملية يجب أن تكون إشارات التحكم كما في الحالة (3) لجدول إشارات الانتخاب، وعليه قمنا بتحديد إشارات المداخل على المحاكي كما في الشكل (26).

الشكل(26): قيم المداخل واشارات التحكم لدارة وحدة الحساب والمنطق لاختبار العملية B.A

وبإجراء المحاكاة كانت النتيجة كما في الشكل (27)، حيث outfinal هي إشارة خرج الناخب وهي A·B ، و التأخير الكلى للإشارة 3.25.

الشكل(27):نتيجة محاكاة دارة وحدة الحساب والمنطق لاختبار العملية B.A

#### 4-7 محاكاة العملية A or B:

لكي نحصل على هذه العملية يجب أن تكون إشارات التحكم كما في الحالة (4) لجدول إشارات الانتخاب، وعليه قمنا بتحديد إشارات المداخل على المحاكى كما في الشكل (28).

| <          | A 🔀          |

|------------|--------------|

| <          | В 🔀          |

| <b>7 √</b> | B-inc-dec 🎛  |

| <b>7 √</b> | A-inc-dec 🔀  |

| <          | Cin 🔀        |

| <          | addnot/sub 🎛 |

| <          | S0 🚼         |

| <          | S1 🔀         |

| <          | S2 🔀         |

الشكل(28): قيم المداخل واشارات التحكم لدارة وحدة الحساب والمنطق لاختبار العملية A or B.

وبإجراء المحاكاة كانت النتيجة كما في الشكل (29)، حيث outfinal هي إشارة خرج الناخب وهي AorB ، و التأخير الكلي للإشارة 3.25.

الشكل(29):نتيجة محاكاة دارة وحدة الحساب والمنطق لاختبار العملية A or B

#### $\overline{A}$ محاكاة العملية

لكي نحصل على هذه العملية يجب أن تكون إشارات التحكم كما في الحالة (5) لجدول إشارات الانتخاب، وعليه قمنا بتحديد إشارات المداخل على المحاكي كما في الشكل (30).

|              |     |     |            |     |            |     |            | _ |           | _ |              |              |

|--------------|-----|-----|------------|-----|------------|-----|------------|---|-----------|---|--------------|--------------|

| <b>√</b>     |     | ✓   | ✓ 🗌        |     | ✓          |     | <b>7</b> 🗆 | ✓ | ✓         |   | ✓            | A 🔀          |

|              |     |     |            |     |            |     |            |   |           |   | 4            | В 🔀          |

| $\checkmark$ | < < | ✓   | <b>√</b>   | < < | <b>√ √</b> | ✓ . | 7          | ∢ | ✓         | ⋖ | ✓            | B-inc-dec 🎇  |

|              |     |     |            |     |            |     |            |   |           |   | ✓            | A-inc-dec 🔀  |

|              |     |     |            |     |            |     |            |   |           |   | 4            | Cin 🎇        |

| $\checkmark$ | 4   | ✓   | <b>√</b>   | < < | <b>√ √</b> | ✓.  | 7          | ∢ | ✓         | ⋖ | 4            | addnot/sub 🎇 |

|              |     |     |            |     |            |     |            |   |           |   | 4            | S0 🚼         |

|              |     |     |            |     |            |     |            |   |           |   | 4            | S1 🚼         |

| $\checkmark$ | < < | ✓ [ | <b>√ √</b> | < < | ✓ ✓        | <   | 7          | ✓ | <b></b> ✓ | ⋖ | $\checkmark$ | S2 🚟         |

$\overline{A}$  الشكل (30): قيم المداخل واشارات التحكم لدارة وحدة الحساب والمنطق لاختبار العملية

وبإجراء المحاكاة كانت النتيجة كما في الشكل (31)، حيث outfinal هي إشارة خرج الناخب وهي إشارة  $ar{A}$ ، و التأخير الكلى للإشارة 3.25.

$\overline{A}$  الشكل (31):نتيجة محاكاة دارة وحدة الحساب والمنطق لاختبار العملية

## 4-9 محاكاة العمليات السابقة في الوقت نفسه:

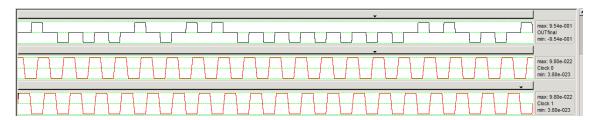

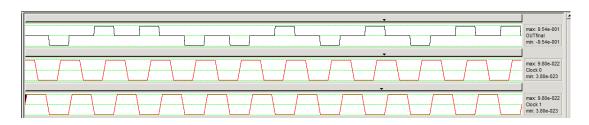

لمحاكاة العمليات معاً سنقوم بإعطاء قيم مختلفة لإشارة الانتخاب وذلك لدراسة جميع الحالات وبناء على ذلك قمنا بتحديد قيم إشارات الدخل كما في الشكل (32)، بحيث تشمل القيم الثمانية الأولى جميع حالات إشارات الانتخاب ويوضّح الشكل(33) نتيجة المحاكاة حيث حصلنا على إشارة الخرج الصحيحة وفقاً لخطوط الانتخاب.

الشكل(32): قيم المداخل وإشارات التحكم لدارة وحدة الحساب والمنطق الختبار جميع العمليات

الشكل(33):نتيجة محاكاة دارة وحدة الحساب والمنطق لاختبار جميع العمليات

# 5 - الاستنتاجات والتوصيات:

تضمّن النموذج في الدراسة [4] ثلاث وظائف اثنتان حسابيتان وهي نصف الجامع ونصف الطارح ووظيفة منطقية واحدة وهي وظيفة and ، بينما قمنا بإنجاز تصميم وحدة حساب ومنطق موسّعة حيث تضمّنت أربع عمليات حسابية وأربع عمليات منطقية. بالإضافة إلى أنّ عمليتي الجمع والطرح كاملتان (مع استعارة وحمل) وبالتالي فإن تصميمنا المقترح أشمل من التصميم المقترح في هذه الدراسة، في حين تضمنت الدراسة [5] العمليات الموضّحة في الجدول الآتي:

الجدول (5): العمليات التي تقوم بها وحدة الحساب والمنطق المقترحة في الدراسة [5]

| Operations | Mode | S1 | S0 | Cin | OUT           |

|------------|------|----|----|-----|---------------|

|            | 0    | 0  | 0  | ×   | A ⊕ B         |

| Logical    | 0    | 0  | 1  | ×   | $A^{\wedge}B$ |

|            | 0    | 1  | 0  | ×   | $A \vee B$    |

|            | 0    | 1  | 1  | ×   | A'            |

|            | 1    | 0  | 0  | 0   | A             |

|            | 1    | 0  | 0  | 1   | A+1           |

|            | 1    | 0  | 1  | 0   | A-1           |

| Arithmetic | 1    | 0  | 1  | 1   | A             |

|            | 1    | 1  | 0  | 0   | A+B           |

|            | 1    | 1  | 0  | 1   | A+B+1         |

|            | 1    | 1  | 1  | 0   | A+B'          |

|            | 1    | 1  | 1  | 1   | A-B           |

- - - -

والتي اعتبرت ضمن الدراسة 12 عملية على الرغم من وجود عمليات مكررة وعمليات محددة بقيمة ال cin والتي يمكن اختيارها للوصول إلى الوظيفة المنطقية المطلوبة، تستطيع الوحدة المقترحة في سياق بحثنا القيام بجميع العمليات السابقة وبمرحلة واحدة ما عدا العملية 'A+B والتي يمكن القيام بها باستخدام الوحدة المقترحة على مرحلتين كما تستطيع القيام بعمليات إضافية هي B-1-B-1-B+1-B-1.

تم في هذه الدراسة [5] فصل وحدتي الحساب والمنطق عن بعضهما واستخدام ناخبين 4X1 لاختيار الوظيفة الحسابية أو المنطقية المطلوبة ومن ثم ناخب 2X1 للاختيار بين خرج وحدة الحساب أو خرج وحدة المنطق، بينما استفدنا في بحثنا من وجود عمليات مشتركة بين الوحدتين ودمجنا الوحدتين معاً، ويوضّح الجدول التالي مقارنة بين هذا التصميم [5] وتصميمنا المقترح من حيث عدد العمليات (مع أخذ جميع حالات الحمل والاستعارة بعين الاعتبار) والمساحة والتأخير و استخدام الطبقات.

الجدول (6): مقارنة بين تصميمنا والتصميم المقترح في الدراسة [5]

| الطبقات     | التأخير | المساحة   | عدد العمليات |                 |

|-------------|---------|-----------|--------------|-----------------|

|             |         |           | غير المكررة  |                 |

| خمس طبقات   | 2.25    | 0.245 µm² | 10           | التصميم [5]     |

| أربعة طبقات | 3.25    | 1.79 µm²  | 13           | التصميم المقترح |

يتفوق تصميمنا المقترح على الدراسات السابقة من حيث عدد العمليات التي يمكنه القيام بها ومن حيث تخفيض عدد الطبقات في حين تتفوق الدراسة [5] على تصميمنا المقترح من حيث تخفيض المساحة والتأخير وهذ أمر متوقع نتيجة الحاجة إلى عدد أكبر من الخلايا والمناطق الزمنية لبناء عدد أكبر من الوظائف ضمن عدد أقل من الطبقات. وتشمل التوصيات:

- تصميم وحدة ضرب/ تقسيم ببيتي دخل وإضافة خرجها كخيار انتخاب سادس إلى وحدة الحساب والمنطق.

- العمل على ضغط التصميم وتخفيض التأخير ضمن نفس العدد من الطبقات.

## 6– المراجع

- [1] BAHAR,A;LAAJIMI,R;ABDULLAH-AL-SHAFI,M;AHMAD,K.2018,Toward Efficient Design of Flip-flops in Quantum-Dot Cellular Automata with Power Dissipation Analysis,International Journal of Theoretical Physics,Vol.57,No.11,3419-3428.

- [2] غانم، يانا. 2020، تصميم محوّل تسلسلي تفر عي/ تفر عي تسلسلي ذو أربع بيتات باستخدام تقنية النقاط الكمومية، مجلة جامعة طرطوس للبحوث والدراسات الهندسية ،المجلد. 14، العدد. 10.

- [3] صالح، سوزي; سقور، علي. 2019، دراسة وتطوير إمكانيات المتحكمات الصغرية وشرائح Arduino في مجال تحصيل المعطيات، مجلة جامعة طرطوس للبحوث والدراسات الهندسية، المجلد. 3، العدد. 5.

- [4] SINGH,A;DUBLISH,A;SHREYASI;NAIK,A.2020,DESIGN AND SIMULATION OF ARITHMETIC LOGIC UNIT USING QUANTUM DOT CELLULAR AUTOMATA,International Journal of Electrical Engineering and Technology,Vol.11,No.3,173-180.

- [5] BABAIE,S;SADOGHIFAR,A;BAHAR,A.2018,Design of an efficient Multilayer Arithmetic Logic Unit in Quantum-dot Cellular Automata.IEEE Transactions On Circuits and Systems II:Express Briefs,Vol.66,No.6,963-967.

- [6] PANDIAMMAL,K;MEGANATHAN,D.2018,Design of 8 bit Reconfigurable ALU Using Quantum Dot Cellular Automata,IEEE 13th Nanotechnology Materials and Devices Conference (NMDC),1-4.

- [7] LENT, C; BERNSTEIN, G. 1993, Quantum cellular automata. Nanotechnology.USA, Vol. 4,No.1,49.

- [8] AHMAD,F;MUSTAFA,M;WANI,N;MIR,F,A novel idea of pseudo-code generator in quantum-dot cellular automata(QCA),International Journal for Simulation and Multidisciplinary Design optimization.Vol.5,A04.

- [9] MUSTAFA,M;BEIGH,M.2014,Novel linear feedback shift register design in quantum-dot cellular automata.Indian Journal of Pure and Applied Physics(JPAP).Vol.52,No.3,203-209.

- [10]GHOLAMI,M;ZOKA,S.2018,A novel rising Edge Triggered Resettable D flip-flop using five input majority gate,Microprocessors and Microsystems.Vol.61,327-335.

- [11]SAFOEV,N;JEON,J.2020,Design and Evaluation of Cell Interaction Based Vedic Multiplier Using Quantum-Dot Cellular Automata, electronics. Vol. 9, No. 6, 1036.

- [12] SHIN,S;JEON,J;YOO,K.2014,Design of Wire-Crossing Technique Based on Difference of Cell State in Quantum-Dot Cellular Automata,International Journal of Control and Automation.Vol.7,No.4,153-164.

- [13] ARALIKATTI,S.2020,QCADesigner: A Simulation and Design layout Tool for QCA based Nano Domain Computing Architectures, Proceedings of the Second International conference on Inventive Research in Computing Applications (ICIRCA-2020), 1042-1046.

- [14] 10 september.2019. <a href="https://waluslab.ece.ubc.ca/qcadesigner/">https://waluslab.ece.ubc.ca/qcadesigner/</a>.

- [15] VERMA,R;MEHRA,R.2013,CMOS Based Design Simulation of Adder/Subtractor Using Different Foundries,International Journal of Science and Engineering.Vol.2,No.1,22-27.

- [16] صالح، سوزي. 2020، تصميم وتحليل أداء دارة جامع كامل متسامح العطل باستخدام تقنيتي CMOS و GDI، مجلة جامعة طرطوس للبحوث و الدر اسات العلمية المجلد. 4، العدد. 4.

- [16] SAFOEV,N;JEON,J.2020,A novel controllable inverter and adder/subtractor in quantum-dot cellular automata using cell interaction based XOR gate,Microelectronic Engineering.Vol.222,111197.

- [17]TAMBE,A;BHAKRE,S;KASSA,S.2019,Design and Analysis (2X1) and (4X1) Multiplexer Circuit in Quantum dot Cellular Automata approach, International Journal of Innovative Technology and Exploring Engineering .Vol.8,No.6S3.INDIA,277-281.

- [18] NADOOSHAN,R;KIANPOUR,M.2013,A novel QCA implementation of MUX based universal shift register, Journal of Computational Electronics. Vol.13,No.1,198-210.

- [19]SEN,B;GOSWAMI,M;SIKDAR,B.2015,Towards modular design of reliable quantum-dot cellular logic circuit using multiplexer,Computer&Electrical Engineering.Vol.45,42-54.

[20] ASFESTANI,M;HEIKALABAD,S.2017,A unique structure for the multiplexer in quantum-dot Cellular automata to create a revolution in design of nanostructures,Physica B:Condensed Matter.Vol.512,91-99.